|

|

| |

MULTIPLEXER DIGITALE

Schema di principio

ELENCO COMPONENTI

Alimentazione elettronica veneta 5V, basette di montaggio (porte logiche NOT, NAND, OR, pulsantiera di comando, led di visualizzazione), cavi unifilari di collegamento.

RELAZIONE TECNICA

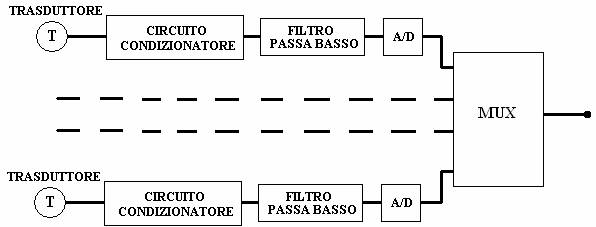

Scopo di questa esperienza è la progettazione di un multiplexer digitale a due linee. In elettronica, un multiplexer è un dispositivo capace di sel 525d37f ezionare un singolo segnale fra diversi applicati in ingresso in base al valore assunto dagli ingressi di selezione (o selettori). Esistono multiplexer sia per segnali digitali che per segnali analogici (amux).Il multiplexer può inoltre essere definito come il dispositivo che permette la condivisone della capacità disponibile di un unico collegamento fra più canali trasmissivi (tecnica di multiplazione). Nella catena di acquisizione dati, il segnale, dopo essere stato pulito e convertito da analogico a digitale, arriva ad un multiplexer digitale, il quale presenta in ingresso i segnali provenienti da più reti di acquisizione. Esso trasferisce così tutti i segnali di ingresso al sistema di elaborazione, rappresentato da un microcontrollore, che acquisisce ed elabora i dati, li trasmette ai dispositivi di uscita e garantisce il controllo del sistema (figura 1):

fig. 1

fig. 1

Il multiplexer è trasparente ad uno dei due ingressi; la sua uscita varia a seconda dell'ingresso attivato dal selettore, ed il dispositivo complessivamente è attivato o disattivato dal segnale di enable.

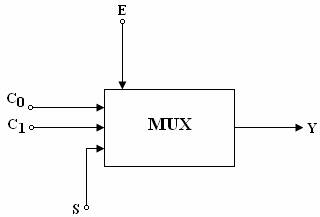

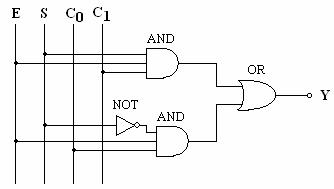

Il nostro multiplexer presenta quindi due segnali di ingresso, che chiameremo C0 e C1, un segnale di selettore S, ed un segnale di abilitazione del dispositivo E. Il tutto può essere rappresentato dallo schema di figura 2:

fig. 2

fig. 2

Il numero degli ingressi che possono essere applicati in corrispondenza di dati selettori è calcolabile come segue:

![]()

Possiamo quindi dire che complessivamente abbiamo tre ingressi: S, C0 e C1, ed una sola uscita, Y. È quindi possibile elaborare la tabella di verità del multiplexer. A tal proposito bisogna ricordare che quando il selettore è a livello logico basso (0) l'uscita Y sarà pari a C0, quando invece è a livello logico alto (1), l'uscita Y sarà pari a C1. Pertanto avremo:

|

S |

C0 |

C1 |

Y |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ovviamente, se il segnale di enable E è a libello logico basso (0) il multiplexer sarà disabilitato, e la sua uscita sarà pari a 0; se invece l'enable è a livello logico alto (1) il multiplexer sarà abilitato, e pertanto presenterà determinati valori in uscita.

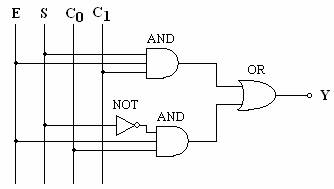

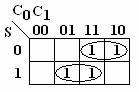

Dalla tabella di verità si può risalire alla mappa di Karnaugh (figura 3), e da quest'ultima allo schema circuitale del multiplexer (figura 4):

![]()

fig. 3

fig. 3

fig. 4

fig. 4

|

Privacy |

Articolo informazione

Commentare questo articolo:Non sei registratoDevi essere registrato per commentare ISCRIVITI |

Copiare il codice nella pagina web del tuo sito. |

Copyright InfTub.com 2024