|

|

| |

Abbiamo già definito cosa intendiamo per grandezza analogica o digitale. Vediamo ora nel caso di un'implementazione vera e propria come si realizzano praticamente i due livelli logici.

Noi ci riferiamo a circuiti elettrici. La grandezza che normalmente si utilizza è, dal punto di vista esterno , una fascia di livelli di tensione.

Quasi tutti i sistemi logici hanno una sola alimentazione, normalmente positiva

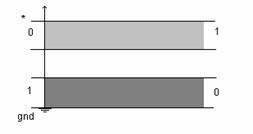

Fa eccezione a questa affermazione la famiglia logica ECL che ha il seguente tipo di alimentazione:

Ma l'ECL è una logica NON SATURATA che per ora non ci interessa (che ha il suo maggiore impiego nella realizzazione di applicazioni veloci).

Le due fasce di valori che rappresentano lo 0 e l'1 logico possono essere o un insieme di valori vicini alla tensione di alimentazione o un insieme di valori vicini a GND.

Posso fare due scelte, la prima è quella di associare all'1 logico una fascia vicina a Val e allo zero una fascia vicina a GND, in questo caso si parla di LOGICA POSITIVA, mentre la seconda è la scelta opposta, cioè si associa lo zero logico a una fascia di valori vicina a Val mentre si associa l'uno logico a un insieme di valori vicini a GND e in questo caso parleremo di LOGICA NEGATA*.

Normalmente, salvo eccezioni, noi lavoreremo in logica positiva.

Sui cataloghi, al fine di evitare confusioni sul tipo di logica utilizzata i due livelli logici vengono indicati con H (high) e L (low).

Vediamo ora quale è il valore comunemente utilizzato per la tensione di alimentazione.

Nella stragrande maggioranza dei casi Val è uguale a 5 V, 15 V o 3.3V.

Perché 5V? Perché all'inizio non c'erano livelli di tensione compatibili e ogni casa utilizzava un suo standard. Successivamente, tra tutte le varie famiglie logiche si è affermata la famiglia logica TTL (Transistor Transistor Logic) che usava un'alime 121b15b ntazione di 5 volt, quindi i nuovi componenti sono stati resi compatibili con questo tipo di logica.

I 15V nominali sono invece l'alimentazione tipica per la famiglia CMOS serie 4000, integrati nati per esigenze spaziali, per circuiti da montare su satelliti, sono integrati ancora prodotti in quanto sono gli unici a essere omologati per l'uso spaziale.

Oggi come oggi comunque anche le nuove serie CMOS funzionano con una tensione di alimentazione di 5V.

Il 3.3V è una tensione nuova utilizzata a partire dal 1992 per i circuiti del tipo Low Voltage CMOS, viene utilizzata per minimizzare la potenza. Il valore di gran lunga più utilizzato rimane comunque il 5V nominali.

Abbiamo detto però che l'uno logico è una fascia di valori vicino ai 5V e lo zero vicino agli 0 V. Dobbiamo vedere come definire queste fasce, dal momento che è fondamentale poter collegare insieme i componenti in modo tale che si possano scambiare segnali interpretandoli correttamente.

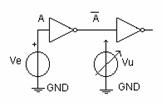

Prendiamo un elemento logico che realizzi la funzione NOT, detto inverter

![]()

Dato l'ingresso misuro Vu.

Partiamo da una tensione di ingresso nulla e facciamo variare Ve. Per un po' non succede nulla, fino a un certo punto in cui l'uscita cambia e rimane tale anche se diminuisce Ve.

|

|

Voh = V output high Vol = V output low

Vih = V input high Vil= V input low

Voh è il valore della tensione di uscita quando in ingresso c'è uno zero logico. Vol è la tensione in uscita quando in ingresso c'è un uno logico.

Vil è il massimo valore di Ve considerato zero logico. Vih è il minimo valore di Ve considerato uno logico.

Iniziamo a individuare le fasce per quanto riguarda l'INGRESSO.

|

|

Abbiamo definito l'ingresso. L'uscita inoltre deve poter pilotare un altro ingresso. Affinché si possa fare il collegamento si deve avere che:

Voh>Vih e Vol< Vil

Ciò deve valere anche nelle condizioni peggiori, quindi:

Vol min > Vih max

Vol max < Vil min

La differenza Voh-Vih si dice margine dell'uno mentre Vil-Vol si dice margine dello zero.

La fascia intermedia dove si ha la commutazione si dice FASCIA DI RUMORE.

Per la famiglia TTL i margini dell'uno e dello zero sono 400mV in quanto Vol=0.4 V Vil=0.8V Vih=2V Voh=2.4V. La fascia di rumore è di circa 1.2V.

I margini dell'uno e dello zero nelle famiglie CMOS e derivati sono leggermente più ampi.

Comunque 400 mV non sono molto considerando gli assorbimenti impulsivi, dobbiamo quindi filtrare opportunamente le alimentazioni, in modo da evitare disturbi eccessivi. (cfr. 1.4.5).

Sono fondamentali per il funzionamento corretto dei circuiti elettrici. Esse mostrano i ritardi di propagazione. Se la macchina è lenta questo fattore non interviene mentre per macchine veloci è rilevante.

Il problema è importante perché si gioca sull'ordine di pochi nanosecondi.

Vediamo quali sono i principali tempi da rispettare.

|

|

Se un segnale passa da un livello a un altro (livelli di tensione o di corrente) con un andamento di questo tipo, si può definire il TEMPO DI SALITA come il tempo che impiega il segnale a passare da 0.1 DV allo 0.9 DV. Il modo con cui varia il segnale non influisce sulla definizione del tempo di salita.

|

|

In modo analogo il TEMPO DI DISCESA è il tempo che impiega il segnale a passare dallo 0.9 DV allo 0.1 DV.

|

|

Se il segnale sale e scende, deve rimanere stabile per un certo tempo significativo rispetto ai tempi di salita e di discesa. I tempi tr e tf devono essere almeno di un ordine di grandezza inferiori rispetto al tempo in cui il segnale rimane stabile.

Inoltre, se si hanno fronti rapidi in una forma periodica come un'onda quadra, applicando lo sviluppo di Fourier si ottengono delle armoniche elevate, quindi ci vogliono bande passanti molto ampie.

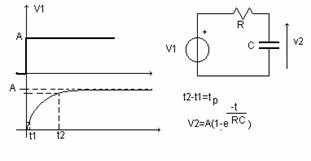

ESEMPIO: Supponiamo di avere un gradino perfetto da applicare a un circuito RC

Calcoliamo per questo segnale il tempo di salita:

tr = 0.35 / f , con questa formula, dato tr ,si ricava la massima frequenza a cui il sistema deve poter rispondere. Visto che Ln 9 ~ 2 R*C deve essere della metà dei tempi di salita, e avendo dei tempi dell'ordine dei nanosecondi i valori di capacità saranno sull'ordine dei pico farad.

Quindi per andare veloce devo avere resistenze piccole quindi correnti elevate, ma correnti elevate devono arrivare da tensioni di alimentazione e V * I = P quindi nei circuiti veloci si dissipano alte potenze.

Date le capacità parassite presenti nei circuiti per andare veloce devo aumentare la corrente, quindi diminuire le resistenze e di conseguenza aumentare la potenza dissipata.

Data una certa disponibilità di corrente per andare veloce devo diminuire le capacità parassite quindi migliorare tecnologicamente i circuiti.

Tra i 2 metodi bisogna trovare il giusto compromesso.

In definitiva i problemi di velocità sono strettamente legati a due fattori:

Come sono realizzati i circuiti quindi alle capacità parassite.

Per andare veloce ho bisogno di correnti alte basse resistenze e, a parità di tensioni in gioco, potenze elevate.

Diamo ora definizioni di tempi legati tipicamente ai circuiti logici.

Supponiamo di avere un circuito logico schematizzato come segue:

Lavoriamo con un blocco combinatorio, l'uscita segue il segnale di entrata DOPO UN CERTO TEMPO DI RITARDO.

ESEMPIO: CASO IDEALE:

In realtà non si ha una situazione del genere, avrò un tempo di propagazione dei segnali detto td o tp (d = delay , p = propagation)

Nel caso reale, invece, si ha:

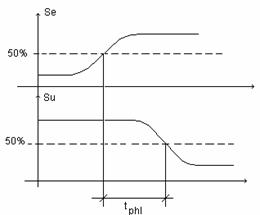

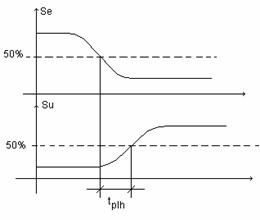

Il tempo di ritardo si riferisce al 50% del salto. In particolare quello scritto si dice tphl, cioè tempo di ritardo per una variazione da alto a basso dell'USCITA.

tplh tempo di propagazione da basso a alto dell'USCITA.

Quando

non è specificato uno dei due casi ci si riferisce al tempo di propagazione

medio: ![]()

Abbiamo quindi due tempi di ritardo a seconda del tipo di transizione. La distinzione è legata al fatto che la parte di circuito che gestisce il segnale di uscita è un circuito composito, ci sono cioè componenti che agiscono sui segnali alti e componenti che agiscono sui segnali bassi, quindi il comportamento durante le due transizioni risulta differente.

|

|

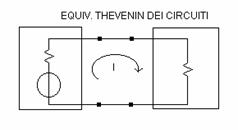

Didatticamente possiamo immaginare una struttura di questo tipo per lo stadio finale di un circuito

La cifra che valuta il comportamento di una famiglia logica ( a parità di funzione di un dispositivo) è il prodotto Pd * tp dove Pd è la potenza dissipata. [tp * Pd] = Joule.

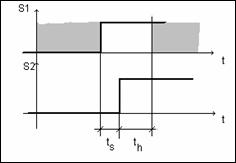

Supponiamo un sistema con due segnali

![]()

Assumiamo che il segnale due venga usato per sincronizzare il comportamento del sistema ( un clock)

Come deve essere il legame di variazione di S1 rispetto a S2?

Per un certo tempo prima la transizione del Ck e per un certo tempo dopo la transizione di CK S1 si deve mantenere stabile e costante.

tsu = TEMPO DI SETUP

th = TEMPO DI HOLD

tsu deve essere rispettato al fine che il circuito sappia cosa fare, si trovi cioè in condizioni stabili ( la sua definizione è univoca).

Il th presenta invece due definizioni diverse a seconda che si ragioni su circuiti bistabili come i flip-flop o sulle memorie. Nel caso dei f-f th deve essere rispettato dal segnale per fare funzionare correttamente il circuito, invece nel caso delle memorie, i tempi di hold ci sono imposti dal circuito e noi li subiamo.

L'incompatibilità tra le famiglie può non essere dovuta alle tensioni : tensioni compatibili non impediscono un'eventuale incompatibilità dovuta alle correnti.

Quindi non è sufficiente definire le tensioni : è necessario considerare anche io margini che riguardano le correnti.

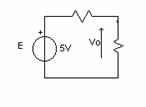

Consideriamo quindi, in un caso specifico, le correnti in gioco e siano positive le I entranti e negative quelle uscenti secondo la convenzione dei doppi bipoli.

Saremmo portati a dire che Ioh = Iih e Iol = Iil ciò non è vero, perché Ioh e Iol sono le correnti che l'elemento a monte è in grado di erogare o assorbire rispettando i margini di zero e di uno.

Se l'elemento a valle non vuole corrente va bene, se ne vuole ho questi limiti da rispettare per mantenere inalterata la logica.

Se V0 deve essere maggiore di 3 posso trovare la massima corrente che può circolare.

Iih e Iil sono invece le correnti che un ingresso PRETENDE quando si trova rispettivamente a livello alto o a livello basso.

Deve sempre essere verificato che:

| Ioh | > | Iih | | Iol | > | Iil |

In modo tale da poter realizzare collegamenti del tipo:

Si definisce FAN OUT = min ( Nh, Ne ) dove:

![]()

![]()

Le porte TTL avevano un fan out di 10, cioè con una porta potevo pilotare 10 altre porte della stessa famiglia.

Il FAN OUT ha senso con elementi della stessa famiglia.

Questo tipo di ragionamento prescinde dall'implementazione. Infatti, ad esempio nelle porte CMOS, le Iih e Iil sono nulle ma il FAN OUT rimane perché una CMOS si comporta come un condensatore per ciò che riguarda l'ingresso e il condensatore impiega un certo tempo a caricarsi, quindi durante i transitori ci sarà della corrente.

Alla base del concetto di famiglia logica sta il concetto di MODULARITA`. Cioè viene pensato un circuito elementare, lo si realizza, e viene utilizzato come cella elementare per realizzare gli elementi più complessi, sempre usando lo stesso circuito di base.

Normalmente il blocco elementare implementa le funzioni logiche elementari AND OR o NOT e attraverso queste, avendo a disposizione NOT-AND o NOT-OR si possono realizzare tutte le altre funzioni logiche più complesse.

I dispositivi di tipo TTL (Transistor Transistor Logic), RTL (Resist Transitor Logic), DTL (Dyod Transistor Logic) si basano sulla cella elementare NAND (la prima lettera indica i componenti del circuito in ingresso, la seconda in uscita); quelli delle famiglie CMOS sulla funzione NOR.

Non è detto almeno nelle prime famiglie che i componenti fossero integrati. La prima a essere integrata fu la DTL. Quella che richiede INDISPENSABILMENTE líntegrazione è la TTL. La DTL è stata la famiglia di passaggio.

La TTL è stata la famiglia che ha condizionato lo sviluppo di tutte le altre famiglie ; la ditta che ha imposto la TTL nel mondo è la TEXAS, che ne ha prodotto due serie:

74 xx NN 0 70° C (quindi per applicazioni commerciali)

54 xx NN -55 110 °C (per applicazioni militari)

La xx indica la tecnologia con cui i componenti sono realizzati. La prima serie ormai scomparsa non aveva lettere.

( fine anni '60) L Low Power

H High Speed

Stretti parenti delle famiglie di base, cambiano solo i valori delle resistenze che sono nella L elevate, nella H basse. L è più lenta ma consuma meno, H è più veloce ma dissipa di più.

(fine anni '70) S Schottky

LS Low power Schottky

Fanno comparire all'interno dei circuiti un elemento nuovo: il diodo Schottky. Non sono cambiate le maschere, cioè il processo di costruzione.

(anni '80) AS Advanced Schottky

ALS Advanced Low power Schottky

F Fast

Sono nuovi prodotti e le TTL di questo gruppo sono attualmente le più diffuse. Anziché aumentare le correnti per ottenere una maggior velocità, si è affinata la tecnologia, riuscendo, intervendo sulla fase di metallizzazione , ad abbassare il valore delle capacità parassite.

La migliore famiglia per il rapporto costo - prestazioni è attualmente la ALS

Oggi come oggi la TTL è in declino anche se i suoi parametri rimangono.

NN indicano i vari circuiti 00=NAND, ad es. 74 xx 00 è un integrato con 4 porte NAND a due ingressi.

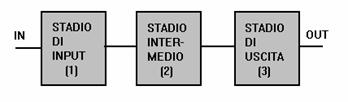

La famiglia TTL, come molti altri dispositivi è composto internamente da più elementi detti STADI. In particolare, per ciò che riguarda la TTL, si possono identificare 3 stadi denominati rispettivamente:

1) Stadio di ingresso

2) Stadio intermedio

3) stadio di uscita

Quindi un qualsiasi dispositivo TTL può essere rappresentato con il seguente schema a blocchi

Nella TTL i primi due stadi sono sempre alimentati mentre lo stadio di uscita si può rappresentare con il seguente modello:

|

|

Il primo si riferisce al caso statico in cui uno solo dei due interruttori si chiude per portare l'uscita o a livello alto e verso massa, mentre il secondo caso si riferisce a una situazione dinamica, infatti durante la commutazione si hanno momenti in cui entrambi gli interruttori (TRANSISTORI) si trovano a essere chiusi.

Quindi la TTL presenta un assorbimento praticamente costante staticamente in quanto il primo e il secondo stadio sono alimentati, mentre presentano un assorbimento di tipo impulsivo in corrispondenza delle commutazioni.

Questo fenomeno è causa di notevoli disturbi e per questo ogni dispositivo deve essere filtrato mediante un condensatore (tipicamente del valore di 10nf) collegato tra l'alimentazione e massa, posto il più vicino possibile all'integrato.

|

|

In generale comunque la TTL assorbe una quantità di corrente costante, in più ci sono i picchi sulle commutazioni.L'assorbimento di corrente e quindi la potenza dissipata cresce con il crescere della velocità della famiglia (dalla TTL normale alle S , AS, F).

Analizziamo ora la curva che indica l'andamento della tensine di uscita in funzione della tensione di ingresso in un dispositivo di tipo TTL che può essere per semplicità un inverter, analizziamo cioè la FUNZIONE DI TRASFERIMENTO DELLA FAMIGLIA TTL.

Individueremo una curva di questo genere:

|

|

Qunado la Vu si avvicina al punto (1) si innesta un fenomeno che velocemente porta alla commutazione della Vu; per questo la TTL è da questo punto di vista la migliore famiglia in commercio. In tuttte le altre famiglie logiche quella zona è lineare e quindi nel punto in cui ci si trova si rimane, non c'è nessun meccanismo che fa crollare a un certo punto la tensione di uscita.

CMOS significa Complementary MOS sono dispositivi che tecnologicamente usano per la loro realizzazione transistori di tipo MOS (Metal Oxid Semiconductor) cioè a semiconduttori metallo e ossido di silicio che possono essere realizzati o con canale di tipo N o con canale di tipo P. I CMOS sono dispositivi in cui sono presenti sia elementi a canale N che elementi a canale P. I MOS e i CMOS hanno avuto una storia completamente indipendente dalla storia dei transistor BJT e quindi dei dispositivi con tecnologia bipolare. Le due vite si sono unite solo in un secondo momento per ragioni di mercato quando la TTL si è affermata come standard con i suoi parametri e anche le famiglie MOS si sono dovute adeguare ad essi per poter sopravvivere. In particolare i circuiti CMOS sono stati studiati al fine di realizzare circuiti a BASSO CONSUMO DI POTENZA STATICA e con flessibilità nel valore della tensione di alimentazione. (Sono nati quasi esclusivamente per esigenza in applicazioni aerospaziali in cui servivano bassi consumi e una flessibilità sull'alimentazione dovuta alla non stabilità dell'energia fornita dalle celle solari).

E` una famiglia nata del tutto incompatibile con la TTL.

Essenzialmente uno stadio CMOS, didatticamente si può modellare con due interruttori come segue:

|

|

La differenza dalla famiglia TTL è che uno solo degli interruttori può essere chiuso in quanto uno è realizzato con un transistore canale N, l'altro con un transistore canale P che sono due strutture complementari. Quindi in condizioni statiche non ho assorbimento di corrente in quanto non ho mai un cammino tra Vcc e GND, tranne al più la corrente richiesta da un eventuale carica.

La conclusione del discorso è che il CMOS non dissipa potenza STATICA.

(Es per una porta NAND in condizioni statiche l'assorbimento è di pochi pA).

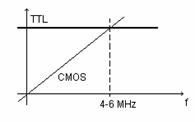

Vediamo ora cosa succede quando facciamo avvenire una commutazione. Succede che la potenza che viene richiesta cresce proporzionalemnte con la frequenza della commutazione.

Non è vero che i CMOS non dissipano potenza, non dissipano POTENZA STATICA.

Se faccio lavorare 2 circuiti equivalenti uno di tipo TTL e uno di tipo CMOS a una frequenza di 4-6 MHz, essi dissipano la stessa potenza, ma se poi non uso per un certo periodo il circuito allora il CMOS non dissipa mentre il TTL continua ad assorbire corrente.

I CMOS sono circuiti a BASSO CONSUMO STATICO

Dato un certo circuito composto da molti componenti, non tutti saranno impegnati contemporaneamente, quindi mediamente si rileva che un circuito complesso realizzato in logica CMOS consuma meno di uno TTL.

|

Privacy |

Articolo informazione

Commentare questo articolo:Non sei registratoDevi essere registrato per commentare ISCRIVITI |

Copiare il codice nella pagina web del tuo sito. |

Copyright InfTub.com 2025