|

|

| |

Relazione Di Controlli

I.P.S.I.A. Iglesias G.Ferraris

Relazione numero 2

I latch

Circuiti di misura utilizzati:

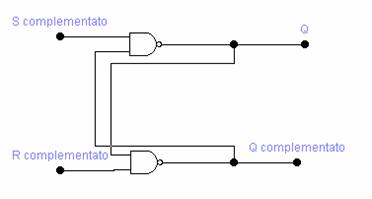

Latch Con porte Nand attivo basso

|

S com |

R com |

Q |

Q com |

|

|

|

|

|

|

|

|

|

|

|

|

|

mem |

|

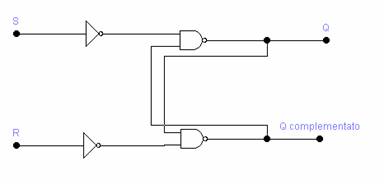

Latch con porte nand attivo alto

|

s |

r |

q |

q com |

|

|

|

|

|

|

|

|

|

|

|

|

|

mem |

|

|

E |

S |

R |

Q |

q com |

|

|

|

|

Mem |

Mem |

|

|

|

|

Mem |

Mem |

|

|

|

|

Mem |

Mem |

|

|

|

|

Mem |

Mem |

|

|

|

|

Mem |

Mem |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

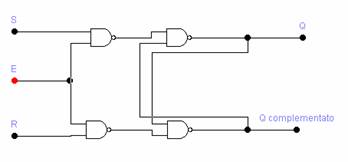

Latch SR con enable

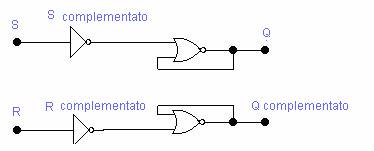

Latch con porte nor attivo alto

|

S |

R |

Q |

Q com |

|

|

|

|

|

|

|

|

|

|

|

|

|

mem |

|

Latch con porte nor attivo basso

|

S |

R |

Q |

Q com |

|

|

O |

|

|

|

|

|

|

|

|

|

|

mem |

|

Cenni Teorici

Un latch è un dispositivo in grado di memorizzare un bit di

informazione. Si chiama latch (catturare) perché è capace di catturare

il livello del segnale d'ingresso e di mantenerlo in memoria. Che differenza c'è fra latch senza abilitazione e

con abilitazione?

Nei primi cambiando le configurazioni attive degli ingressi varierà l'uscita. Nei secondi si può inibire l'effetto

degli ingressi sulle uscite in dipendenza di un segnale di abilitazione. Se il

segnale di abilitazione viene portato a livello attivo solo in determinati

intervalli di tempo, di durata tanto breve da poterli considerare impulsi

istantanei (treno d'impulsi: vedi figura), si otterrà un dispositivo che

potrà cambiare di stato solo in corrispondenza di tali istanti.

Partendo allora dai latch con abilitazione si potranno ottenere dei circuiti

con funzionamento sincronizzato, in cui cioè il cambiamento di stato

delle diverse uscite avviene su comando di un segnale di sincronismo

(clock). Qual è il simbolo di un

latch senza abilitazione? Sono possibili due

configurazioni: latch a porte NOR e a porte NAND.

Il primo ha ingressi attivi alti, il secondo ha ingressi attivi bassi.

Il simbolo di entrambi è indicato in figura

Il simbolo pone in evidenza che in un caso gli ingressi S = Set (mandare ad 1) ed R = Reset (mandare a 0) sono attivi alti, cioè agiscono sull'uscita, settandola o resettandola, quando sono a livello alto. Nell'altro caso (S, R) sono attivi bassi. Il simbolo indica inoltre la presenza di due uscite: una principale, indicata con Q, e l'altra, complementare alla precedente, indicata con Q. Come viene realizzato un latch a porte NOR? Qual è il suo funzionamento? Lo schema utilizzato è quello di figura:

Il comportamento del circuito è quello indicato in tabella:

|

S |

R |

|

Q |

|

|

|

|

memoria |

|

|

|

|

0 reset |

|

|

|

|

1 set |

|

|

|

|

proibita |

1) La configurazione SR=00

(S=0, R=0) è una configurazione di memoria. Ovvero l'uscita Q mantiene il suo

valore.Supponiamo infatti che sia Q=0 (Q è l'uscita della seconda porta, quella

in basso). Tale valore viene riportato all'ingresso della prima porta che

avendo 00 agli ingressi fornisce Q =1 alla sua uscita.

Tale 1 viene riportato all'ingresso della seconda porta, che avendo 01 ai suoi

ingressi conferma il valore 0 alla sua uscita.

Analogo discorso vale se si suppone Q=1.2) La configurazione SR=01 (S=0,R=1)

è la configurazione di reset: essa cioè porta l'uscita a livello basso.

Si noti infatti che porre un 1 all'ingresso di una NOR forza la sua uscita a

zero (quale che sia l'altro ingresso). Quindi Q=0. Tale 0 viene riportato

all'ingresso della prima porta (quella in alto) che darà un 1 alla sua uscita.

Analogamente si capisce che la configurazione simmetrica della precedente

(SR=10) produrrà uscite simmetriche rispetto al caso precedente (Q=1, Q=0).

3) La configurazione 10 setta allora il dispositivo, cioè ne porta l'uscita

principale a livello alto.4) Infine la configurazione SR=11 è una

configurazione PROIBITA, poiché entrambe le uscite Q

e Q verrebbero forzate al livello 0, e quindi non sarebbero l'una

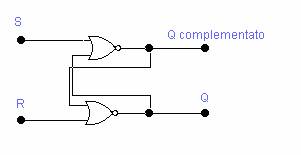

complementare dell'altra come richiesto.Qual è la struttura di un latch a porte NAND? Qual è il suo

funzionamento? La struttura è analoga a quella

del latch a porte NOR, con la differenza che adesso si utilizzano

porte NAND e l'uscita principale Q si prende sulla prima porta (quella

in alto).

Osserviamo la figura.

Come si vede,

gli ingressi sono indicati adesso con S, R per segnalare che sono

attivi bassi. Infatti è noto che una NAND se ha uno dei due ingressi a 0

porta la sua uscita ad 1.

Allora se entrambi gli ingressi sono a 0, entrambe le uscite andranno ad 1

(e questo è da evitare: configurazione proibita). Se invece uno solo degli

ingressi è a zero l'uscita corrispondente andrà ad 1 (SR=01 sarà allora la

configurazione di set, mentre SR=10 sarà la configurazione di reset)

Infine se entrambi gli ingressi sono disattivi (SR=11) l'uscita manterrà il suo

valore (configurazione di memoria). Esistono latch SR

statici (senza

abilitazione) integrati? Si, esistono, anche se sono poco diffusi perché la loro utilità è

limitata. Il tipo più noto è il 279 che contiene quattro latch statici a

porte NOR. Quale può essere una

possibile applicazione del latch statico? Può

essere il circuito antirimbalzo di un interruttore.

Si consideri un interruttore meccanico S che venga azionato per fornire

corrente ad un carico (figura).

In teoria se

l'interruttore viene chiuso all'istante t0, si dovrebbe misurare sul

carico una tensione a gradino. In realtà come mostra la figura, l'uscita, prima

di portarsi al valore di regime, subito dopo t0 presenta delle

oscillazioni che in molti casi possono essere indesiderate.

Per eliminare tale effetto, dovuto ai rimbalzi di S, si può utilizzare un latch

statico con funzione antirimbalzo, come indica la figura:

A riposo l'interruttore si trova in posizione A. Il latch è resettato e l'uscita è bassa. Portando l'interruttore in posizione B il latch viene settato e l'uscita si porta a livello alto. Anche se il latch dopo aver toccato B rimbalza portandosi in una posizione INTERMEDIA fra A e B, il latch si troverà nella configurazione di memoria (SR=11), per cui l'uscita si manterrà alta). Come si può ottenere un latch con abilitazione (gated), partendo da un latch statico? E' sufficiente far precedere un latch nand da due porte nand A,B alle quali si applicano i segnali di set e reset ed un segnale comune di abilitazione del latch (E=Enable) [vedi figura].

Si noti che se

E=0 le due porte d'ingresso bloccano il passaggio dei due segnali di comando

del dispositivo (S,R), perciò il latch si troverà nello stato di memoria.

Se viceversa E=1 i due segnali S,R si trasferiranno a valle delle porte

d'ingresso, divenendo S'R'. Tuttavia avranno un valore INVERTITO rispetto al

loro valore di partenza.

Questo significa che la configurazione SR=00 diventerà S'R'=11 dopo le porte

d'ingresso, e poiché la configurazione 11 è la configurazione di memoria per

il latch nand, ne segue che SR=00 è la configurazione di memoria per il latch

con abilitazione.

Analogamente la

configurazione SR=01 diventerà S'R'=10 a valle delle porte d'ingresso.

Quest'ultima è la configurazione di reset per il latch nand. Allora SR=01=

reset del latch con abilitazione.

La configurazione SR=10 diventerà S'R'=01 (set del latch nand) . Allora SR=10=

configurazione di set. Infine SR=11 si trasforma in S'R'=00 che è la

configurazione proibita per il latch nand.

Allora SR=11= configurazione proibita.

Dimensionamento Componenti

Eseguito dal professore

Scopo dell'esercitazione

|

Privacy |

Articolo informazione

Commentare questo articolo:Non sei registratoDevi essere registrato per commentare ISCRIVITI |

Copiare il codice nella pagina web del tuo sito. |

Copyright InfTub.com 2026