|

|

| |

Se analizziamo uno scambio di dati tra più di due elementi (sia nel caso del microprocessore collegato alle varie periferiche che in quello del computer centrale collegato ad un certo numero di terminali) occorre prevedere nel Protocollo ulteriori regole per distinguere il sistema cui si è collegati.

Due sono i metodi utilizzati per coordinare il trasferimento dei dati:

colloquio sotto il controllo dell'unità centrale (o Polling);

colloquio su richiesta della periferica (o Interrupt).

Chiameremo Master l'unità principale che detiene il controllo del protocollo e Slave i generici elementi collegati.

Polling

Il

Master interroga ciclicamente tutti gli Slave, esaminando per ciascuno un

opportuno registro di stato, in modo da individuare chi è disponibile al

colloquio (in input o in output):

Il

Master interroga ciclicamente tutti gli Slave, esaminando per ciascuno un

opportuno registro di stato, in modo da individuare chi è disponibile al

colloquio (in input o in output):

Se la periferica non è pronta, l'esame passa allo Slave successivo.

Se la periferica è pronta viene effettuato lo scambio dei dati e, al termine, il master riprende l'esame ciclico.

Con questo metodo, detto Polling, l'unità centrale ha il controllo completo dello stato d'avanzamento dei processi, decide di volta, in volta se una periferica deve essere interpellata o no, decide l'ordine di Priorità che può anche cambiare durante il lavoro. Altro vantaggio è la relativa semplicità circuitale e del software di gestione.

Per contro il Master spreca buona parte del suo tempo in interrogazioni spesso inutili degli altri dispositivi. Inoltre, una periferica che si renda disponibile al colloquio subito dopo un'interrogazione con esito negativo, dovrà attendere tutto il ciclo di Polling prima di essere nuovamente interpellata con probabile perdita di dati (ad esempio il registro Rx Hold dell'RS232 che rischia d'essere soprascritto dal prossimo carattere in arrivo sul registro Rx Shift).

Interrupt

Quando il Polling non è utilizzabile per ragioni d'efficienza, viene adottata la tecnica dell'Interruzione di Programma (Interrupt): in questo caso lo Slave che ha necessità di un col 636f51g loquio (o che si è reso disponibile dopo una precedente richiesta del Master) invia all'unità centrale un segnale di richiesta su un apposito canale.

Più in generale per "Interrupt" si intende il verificarsi di un evento esterno che alteri l'esecuzione di un programma.

Il master può decidere se ascoltare o no il segnale d'interrupt (mascheramento) che, in ogni modo, non può interrompere un'istruzione macchina in corso.

Ricevuta la richiesta il master salva sullo Stack le informazioni relative al programma in corso (Program counter, Flags, registri dati).

Viene quindi attivata la procedura di riconoscimento della periferica che ha chiesto il servizio.

In base al tipo di slave viene eseguita una subroutine specifica per trasferire i dati da o verso la periferica.

Al termine del colloquio il master riprende dallo stack i valori parcheggiati e prosegue il programma interrotto.

Con questo tipo di gestione il master può eseguire altri programmi durante le fasi in cui le periferiche sono inattive, intervenendo solo quando è necessario eseguire il trasferimento dei dati. Per contro viene richiesta una maggiore complessità circuitale e, soprattutto, software, per risolvere una serie di problemi aggiuntivi:

Riconoscimento della periferica che inoltrato il segnale di interrupt (escludendo che le richieste pervengano su fili separati per ciascuna periferica) e attivazione della subroutine di servizio relativa.

In caso di contemporaneità di richiesta occorre scegliere quale slave servire per primo assegnando dei livelli di priorità.

Per evitare la nidificazione delle chiamate occorre disabilitare il segnale di interrupt durante l'esecuzione della subroutine di servizio.

Potrebbe essere necessario, durante il lavoro, abilitare selettivamente solo alcune periferiche ed altre no.

Riconoscimento con ciclo di verifica periferiche

La soluzione più semplice consiste nell'attivare, dopo la segnalazione di interrupt, un ciclo di interrogazioni analogo al Polling.

Il master cerca la periferica disponibile al colloquio nell'ordine che ritiene più valido al momento, scavalcando quelle che desidera disabilitare. In caso di verifica positiva viene invocata la subroutine corrispondente e, se il programma lo prevede, il piedino di interrupt viene temporaneamente disabilitato fino al termine del colloquio.

Lo svantaggio di questo sistema è la relativa lentezza da parte dell'unità centrale ad attivare il colloquio.

Daisy chain

Si

tratta di una soluzione hardware che permette di abilitare solo una delle

periferiche che chiedono il colloquio, secondo una priorità prefissata:

Si

tratta di una soluzione hardware che permette di abilitare solo una delle

periferiche che chiedono il colloquio, secondo una priorità prefissata:

tutte le periferiche sono collegate con un unico canale al piedino di interrupt (INTREQ) del master;

quando riceve una richiesta, il master invia un segnale di abilitazione INTACK (Interrupt Ackonowledge);

il segnale di INTACK attraversa in serie una cascata di dispositivi elementari, uno per periferica: ciascuno di questi circuiti lascia passare l'abilitazione se la periferica collegata non ha chiesto il servizio, mentre blocca il segnale abilitando la propria periferica se questa aveva generato il segnale di interrupt;

la periferica abilitata trasmette sul bus dati il proprio codice di riconoscimento;

l'unità centrale in base a questo codice cerca in un elenco l'indirizzo della subroutine di servizio e la esegue.

La tecnica daisy chain permette una gestione semplice ed economica del colloquio in interrupt, con la possibilità di aggiungere altre periferiche alla catena fino al numero massimo consentito dal codice di riconoscimento.

D'altro canto le priorità degli slave sono legate alla collocazione hardware e quindi non sono modificabili (il circuito più vicino al master ha sempre la precedenza); inoltre non è possibile disabilitare selettivamente solo alcune periferiche.

Controllore di interrupt esterno

Controllore di interrupt esterno

Il metodo più versatile per arbitrare le richieste di interrupt è quello di affidare il lavoro ad un dispositivo esterno dedicato.

Nel caso del PC viene usato il controllore PIC 8259 (Programmable Interrupt Controller) che gestisce 8 linee di Interrupt separate; il PIC può essere istruito dal microprocessore in base alle varie esigenze:

ad ogni periferica viene assegnato un codice differente;

viene fissato un ordine di priorità degli otto dispositivi collegati;

il master può chiedere di abilitare selettivamente solo alcune linee;

quando il PIC riceve una segnalazione trasmette sul Bus Dati il codice corrispondente alla periferica;

quando due o più periferiche chiedono di essere servite, il PIC provvede a selezionare quella con priorità più alta;

solo quando il microprocessore, terminato il servizio della periferica, comunica la fine dell'interruzione, il PIC abilita ulteriori richieste.

La gestione degli INTERRUPT nel PC

I processori a 16 bit dell'INTEL prevedono una gestione vettorizzata delle interruzioni: in corrispondenza del segnale INTA, il processore legge il byte basso del bus dati e utilizza il valore letto come puntatore alla tabella di 256 indirizzi di 4 byte ciascuna, posta nella RAM da 00000h a 003FFh.

Ad ogni Interrupt corrisponde l'indirizzo di una Subroutine di gestione (sempre di tipo FAR indipendentemente dal modello di memoria utilizzato dal programma principale); la sequenza delle operazioni eseguite dal mP è:

Termina l'istruzione in corso.

Salva i registri CS, IP e Flag nello Stack.

Acquisisce dal PIC il codice della periferica che ha chiesto l'interrupt.

Legge dalla tabella degli Interrupt i nuovi valori per IP e CS.

Esegue la routine di colloquio con la periferica o di gestione dell'evento.

In uscita dalla Subroutine, con l'istruzione IRET vengono recuperati i Flag e i vecchi valori di IP e CS.

La stessa procedura viene seguita sia per gli Interrupt Hardware (corrispondenti alla richiesta da una periferica) che per gli Interrupt Software (invocato da programma con l'istruzione INT xx )

|

INT |

CS:IP in Tabella a |

Evento concomitante o Funzione Svolta dalla Subroutine |

|

00h |

03h - 00h |

Divisione per 0 |

|

01h |

07h - 04h |

Esecuzione passo-passo del programma |

|

02h |

0Bh - 08h |

NMI ( Interrupt Non Mascherabile ) |

|

03h |

0Fh - 0Ch |

Breakpoint |

|

04h |

13h - 10h |

Overflow |

|

05h |

17h - 14h |

Print Screen |

|

08h |

23h - 20h |

System Timer IRQ0 |

|

09h |

27h - 24h |

Lettura tastiera e inserimento nel buffer : IRQ1 |

|

0Bh |

2Fh - 2Ch |

Colloquio con COM2 : IRQ3 |

|

0Ch |

33h - 30h |

Colloquio con COM1 : IRQ4 |

|

0Dh |

37h - 34h |

IRQ5 |

|

0Eh |

3Bh - 38h |

Controller Floppy disk: IRQ6 |

|

0Fh |

3Fh - 3Ch |

Colloquio con LPT1 : IRQ7 |

|

10h |

43h - 40h |

Gestione del video |

|

14h |

53h - 50h |

Gestione della comunicazione seriale |

|

16h |

5Bh - 58h |

Gestione della tastiera |

|

1Ch |

70h - 73h |

Richiamato dalla sub di INT 8: a disposizione dell'utente |

|

33h |

CFh - CCh |

Gestione del Mouse |

|

70h |

1C3h - 1C0h |

Real Time Clock: IRQ8 |

|

76h |

1DBh - 1D8h |

Controller Hard disk: IRQ14 |

Per collegare più periferiche alla linea INT del microprocessore viene usato il controllore 8259 (Programmable Interrupt Controller) che gestisce 8 linee di Interrupt anche in termini di priorità: quando due o più periferiche chiedono contemporaneamente di essere servite, il PIC provvede a selezionare quella con priorità più alta ed a trasmettere sul Bus Dati un codice corrispondente. Quando il microprocessore termina il servizio della periferica, comunica al PIC la fine dell'interruzione (EOI) in modo da poter abilitare ulteriori Interrupt.

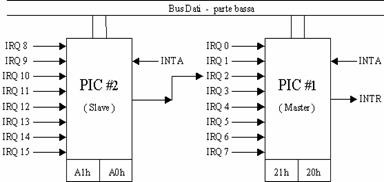

Nei PC di tipo AT e successivi sono presenti 2 PIC (definiti PIC#1 e PIC#2), collegati in cascata ed allocati agli indirizzi 20h-21h e A0h-A1h rispettivamente:

Nella fase di Bootstrap il BIOS provvede a programmare PIC#1 e PIC#2 trasmettendo gli opportuni parametri ai registri 20h-21h e A0h-A1h (priorità delle interruzioni, associazione tra IRQx e Vettore Interrupt, ecc... ).

Gli Interrupt così collegati al piedino INTR del microprocessore possono essere abilitati o disabilitati in blocco agendo sul flag di Interrupt con le istruzioni assembler STI e CLI (gli Interrupt software NON sono mascherabili).

I singoli IRQ possono poi essere abilitati o disabilitati mascherando ciascun bit del registro di indirizzo dispari del PIC (ogni bit corrisponde ad un IRQ) tenendo presente che 0 equivale all'abilitazione mentre 1 equivale alla disabilitazione dell'Interrupt.

Ad esempio, per abilitare la seriale COM2 occorre:

IN AL , 21h

AND AL, 11110111b

OUT 21h, AL

Per resettare la richiesta in corso, al termine della routine di Interrupt,

bisogna inviare il valore 20h all'indirizzo pari del PIC interessato.

MOV AL , 20h

OUT 20h, AL

La gestione del Timer

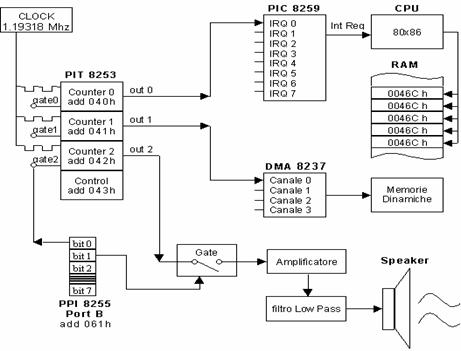

Nel PC è installato il timer PIT 8253/8254 (Programmable Interval Timer) che si occupa di scandire il tempo per i dispositivi interni.

Il PIT è mappato in isolated I/O agli indirizzi 040h ÷ 043h e

riceve in input il segnale prodotto da un clock base di 1193180 Hz; la frequenza

in output è ottenuta decrementando un registro interno a 16 bit, a partire ogni

volta da un valore fissato programmabile, e generando un segnale alto in output

ogni volta che il registro si azzera.

In pratica assegnando al registro un valore 1 si ottiene in output la stessa

frequenza del segnale di ingresso, assegnando 2 si ottiene una frequenza

dimezzata (un periodo raddoppiato) e così via.

La minima frequenza è ottenibile assegnando 0 come valore iniziale, in quanto il segnale di out verrà generato ogni 65536 decrementi del registro base.

Registro di Controllo

Il PIT 8253/8254 può essere programmato scrivendo un byte di controllo nell'indirizzo I/O 043h (registro a sola scrittura) e quindi uno o due byte nei registri dei singoli contatori (lettura/scrittura).

L'accesso ai registri dei singoli contatori è sempre 8 bit alla volta.

|

bit |

|

|

|

|

|

|

|

|

|

043h |

|

|

|

|

|

|

|

|

|

|

select counter 00 = counter 0 01 = counter 1 10 = counter 2 |

read /write successiva operazione di lettura o scrittura sui registri contatori: 01 = solo byte basso 10 = solo byte alto 11 = prima byte basso e dopo byte alto |

mode modalità operativa del PIT, valori da 000 a 101. |

BCD 0 = conteggio a 16 bit da 0h a FFFFh 1 = conteggio BCDdecimale da 0 a 9999 |

||||

Contatore 0

Il valore di partenza del contatore è 0 (ovvero 65536): la frequenza di Out è 1193180 / 65536 = 18.206 Hz.

Il segnale Out 0 è collegato a IRQ 0 del PIC: circa 18 volte al secondo il mP interrompe il lavoro e incrementa la longword 046Ch in memoria, che è stata inizializzata all'atto del bootstrap con il numero dei clock trascorsi dalla mezzanotte precedente (l'orologio di sistema è in funzione anche a PC spento);

quando sono raggiunte le 24:00 ( » 157300 impulsi ) viene incrementato il byte 0470h.

Contatore 1

Il contatore 1 opera con un valore 18, quindi genera una frequenza pari a 66288 Hz: questo segnale viene utilizzato per il refresh delle memorie dinamiche DRAM.

Contatore 2

Il contatore due è utilizzato per generare la frequenza di funzionamento dell'altoparlante interno (Speaker).

Per programmare il contatore 2 occorre attivare la modalità 3 del PIT con conteggio binario:

mov al, 10110110b contatore 2, byte basso e poi byte alto, modo 3, binario

out 43h, al

mov al, low-count

out 42h, al

mov al, high-count

out 42h, al

La gestione dello Speaker

La scala delle note musicali (basata su 440 Hz = LA, e con un Fattore moltiplicativo per un semitono = 1,0594631 pari alla radice 12° di 2 ) viene riprodotta dividendo il Clock base del PC = 1193180 Hz per la frequenza, ed assegnando il divisore al registro 0x42 del counter 0 del Timer, collegato allo speaker.

Ad esempio il LA = 440 Hz viene ottenuto con un divisore .

|

Scala delle note musicali: Clock base del PC = 1193180 / frequenza nota Fattore moltiplicativo per un semitono = 1,0594631 |

|

|

divisore nota frequenza |

divisore nota frequenza |

|

10847 LA 110 10238 LA# 117 9664 SI 123 9121 DO 131 8609 DO# 139 8126 RE 147 7670 RE# 156 7240 MI 165 6833 FA 175 6450 FA# 185 6088 SOL 196 5746 SOL# 208 5424 LA 220 5119 LA# 233 4832 SI 247 4561 DO 262 4305 DO# 277 4063 RE 294 3835 RE# 311 3620 MI 330 3417 FA 349 3225 FA# 370 3044 SOL 392 2873 SOL# 415 2712 LA 440 |

2712 LA 4402560 LA# 466 2416 SI 494 2280 DO 523 2152 DO# 554 2032 RE 587 1918 RE# 622 1810 MI 659 1708 FA 698 1612 FA# 740 1522 SOL 784 1437 SOL# 831 1356 LA 880 1280 LA# 932 1208 SI 988 1140 DO 1047 1076 DO# 1109 1016 RE 1175 959 RE# 1245 905 MI 1319 854 FA 1397 806 FA# 1480 761 SOL 1568 718 SOL# 1661 678 LA 1760 |

La durata della nota viene ottenuta attivando e disattivando il registro 0x61 che funge da Gate per l'amplificatore.

Il filtro Passa-basso esclude frequenze dannose per l'altoparlante.

Attivazione

in al, 61h

or al, 3

out 61h, al

Disattivazione

in al, 61h

and al, 11111100b

out 61h, al

|

Privacy |

Articolo informazione

Commentare questo articolo:Non sei registratoDevi essere registrato per commentare ISCRIVITI |

Copiare il codice nella pagina web del tuo sito. |

Copyright InfTub.com 2025