|

|

| |

Oggetto dell'esercitazione:

VERIFICA DEL FUNZIONAMENTO DEI FLIP-FLOP.

STRUMENTI ADOPERATI

|

Nome dello Strumento |

Simbologia |

Classe |

|

ALIMENTATORE STABILIZZATO. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Accessori adoperati:

№1 Scheda A02;

№1 Scheda E06;

№1 Scheda E07;

№1 Scheda E08;

№1 Resistenza da 470Ω;

Cavetti di collegamento.

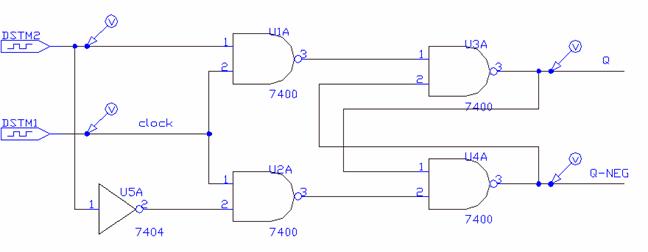

Schema elettrico:

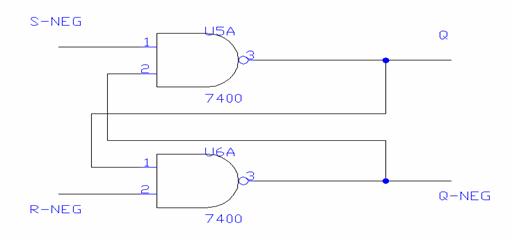

LATCH S\R REALIZZATO CON PORTE NAND.

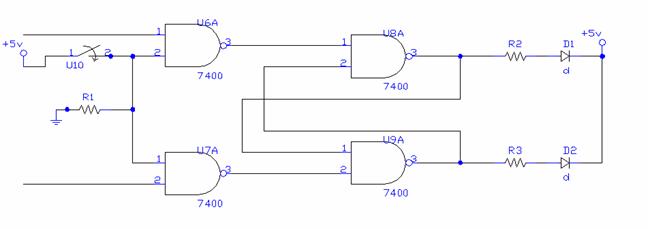

LATCH S\R SINCRONIZZATO REALIZZATO CON PORTE NAND.

LATCH S\R CON CLOCK

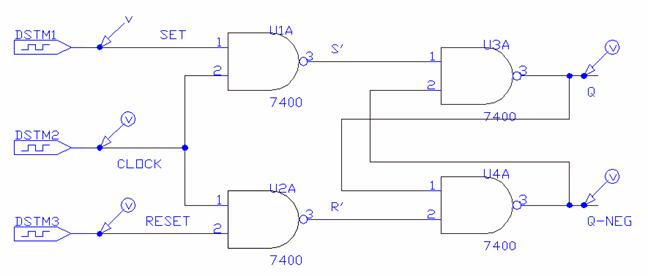

FLIP-FLOP DEL TIPO D.

FLIP-FLOP DEL TIPO D.

Descrizione teorica:

In questa esperienza parliamo dei circuiti logici sequenziali: in questi circuiti le uscite non dipendono solo dagli ingressi ma anche dalla storia passata degli ingressi, in pratica dalle sequenze di avvenimenti logici che si sono succeduti nel tempo agli ingressi. Tali circuiti sono essenziali per creare le cosiddette macchine a stati finiti, che permettono di generare un insieme di stati logici possibili da un'opportuna sequenza d'ingressi, e quindi di eseguire una sequenza d'elaborazioni dipendenti dalla serie d'istruzioni ricevute.

IL LATCH S\R REALIZZATO CON PORTE NAND.

Esso presenta due terminali d'ingresso indicati con S (SET) e R (RESET) su cui è inserita l'informazione da memorizzare e due terminali d'uscita Q e Q-NEG (negato).

Nel circuito sono stati realizzati dei collegamenti di reazione fra l'uscita Q e l'ingresso della porta U5A e fra Q-NEG e l'ingresso della porta U6A.

Il significato degli ingressi S e R (Set & Reset) è il seguente:

Il SET porta l'uscita Q ad 1e Q-NEG a 0 (operazione di Set).

Il RESET porta l'uscita Q a 0 e Q-NEG a 1 (operazione di Reset).

|

S-NEG |

R-NEG |

Qn+1 |

Q-NEGn+1 |

COMMENTO |

|

|

|

|

|

Stato Improprio |

|

|

|

|

|

SET |

|

|

|

|

|

RESET |

|

|

|

Qn |

Q-NEG |

Memoria |

Qui a lato possiamo osservare la tabella di verità: per attivare l'uscita Q occorre che i segnali S e R siano ambedue bassi, lo stato di memoria, in pratica la conservazione dello stato precedente si ha quando S e R sono ambedue alti, mentre quando si verifica che S=R=0 si ha lo stato improprio.

BISTABILI SINCRONIZZATI.

Il tipo di memoria incontrata su descritta funziona a tempo continuo, in pratica in qualsiasi istante di tempo è possibile che il latch cambi stato.

Nella realizzazione di una rete sequenziale è opportuno avere una memoria sincronizzata, il cui stato può variare in corrispondenza di un insieme discreto d'istanti di tempo scanditi da un segnale periodico dette CLOCK.

Esistono quattro tipi di Clock, in base al diverso tipo di tempificazione:

Level-triggered.

Edge-triggered.

Pluse-triggered.

Master-Slave.

LATCH S\R CON CLOCK.

|

CK |

S |

R |

Qn+1 |

Q-NEGn+1 |

COMMENTO |

|

|

X |

X |

Qn |

Q-NEG |

Memoria |

|

|

|

|

Qn |

Q-NEG |

Memoria |

|

|

|

|

|

|

SET |

|

|

|

|

|

|

RESET |

|

|

|

|

|

|

Stato improprio |

Un lacth S\R con clock è provvisto degli ingressi dati più l'ingresso del clock. Rispetto al letch elementare esso presenta altre due porte NAND aggiunte, che nel momento in cui il clock è al livello logico basso impediscono il caricamento del latch, tramite S e R, in quanto S' e R' sono entrambi alti. Al contrario quando il clock è alto, esse si comportano da invertitori e quindi trasformano gli ingressi logici S' e R', attivi alti, nei segnali S e R attivi alti. Nel momento in cui S=1 e R=0 viene effettuato il SET. Quando S=0 e R=1 viene effettuato il RESET. Nel momento in cui S e R sono nulli il bistabile mantiene in memoria lo stato precedente. In questi tipi di latch, sono presenti ancora i problemi rilevati nel latch elementare, vale a dire gli stati impropri.

Questo tipo di problema viene eliminato tramite un altro tipo di latch:

IL D-LATCH LEVEL-TRIGGERED.

Lo stato indesiderato di un latch S|R può essere eliminato imponendo che S e R siano sempre diversi tra loro S=R-NEG. Perciò si pone S=D e R=D-NEG.

Il significato di D è il seguente:

Se D è alto viene caricato il valore 1.

Se D è basso viene caricato il valore 0.

Il flip-flop D contiene due latch in un singolo integrato e presenta:

Un ingresso di clock indicato con C.

Due data input 1D e 2D.

Due output 1Q e 2 Q.

Due uscite complementate 1Q-NEG e 2Q-NEG.

|

C |

D |

Q |

Q-NEG |

COMMENTO |

|

|

|

|

|

Q=D=0 |

|

|

|

|

|

Q=D=1 |

|

|

X |

Q |

Q-NEG |

Data Latched |

Esecuzione della misura e analisi dei dati:

Questa esperienza ha il compito di verificare il funzionamento dei flip- flop in particolare dei latch S\R, latch S\R sincronizzato e del tipo D-Latch level-triggered (o Flip-Flop del tipo D).

Prima di effettuare la prova è stata verificata la funzionalità degli accessori e strumenti adoperati. Dopo di ciò sì è passati all'assemblaggio dei circuiti che è avvenuto seguendo gli schemi elettrici nell'apposita sezione. Per compiere l'assemblaggio sono state usate le schede A02, E06, E07, E08, sulle quali erano montate porte NAND, pulsanti, interruttori, LED.

La fase successiva è stata quella della verifica del funzionamento, che è stata fatta seguendo le specifiche riportate nelle tabelle di verità su riportate ( nella sezione descrizione teorica).

Conclusioni:

Nello svolgimento dell'esperienza si è notato che i circuiti si comportavano esattamente come le specifiche riportate nelle tabelle di verità. In conclusione l'esperienza è stata svolta con esito positivo, poiché le tabelle di verità su riportate sono state verificate con successo.

Giudizio di merito:

Voto

L'Insegnante Realizzata dall'Alunno Antonio NERO

|

Privacy |

Articolo informazione

Commentare questo articolo:Non sei registratoDevi essere registrato per commentare ISCRIVITI |

Copiare il codice nella pagina web del tuo sito. |

Copyright InfTub.com 2026