|

|

| |

Si dicono circuiti sequenziali i circuiti in cui l'uscita dipende dallo stato degli ingressi nell'istante considerato ma anche dallo stato degli ingressi e dell'uscita nell'istante precedente.

Il latch è un elemento elementare 222d33c di memoria e il suo nome deriva quindi dalla proprietà di bloccare, ovvero di conservare, nel tempo, un'informazione.

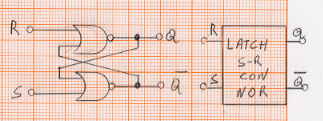

Può essere realizzato con porte NOR o porte NAND, lo schema elettrico con porte NOR è il seguente:

Il latch ha 2 entrate: il SET che pone l'uscita Q a 1, il RESET che pone l'uscita Q a 0.

Esistono due uscite: la Q e la Q negata (che è il complemento della Q).

Tabella di Verità:

|

S |

R |

Qn+1 |

|

|

|

Qn |

|

|

|

|

|

|

|

|

|

|

|

N.V. |

Qn è lo stato dell'uscita prima dell'applicazione dei segnali d'ingresso, Qn+1 è lo stato dell'uscita dopo l'applicazione dei segnali d'ingresso, quando si ha la dicitura Qn+1=Qn allora l'uscita è rimasta invariata (quando è a 0 rimane a 0, quando è a 1 rimane a 1).

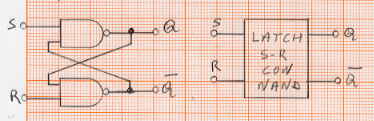

Schema elettrico con porte NAND:

questa invece è la tabella di verità:

|

S |

R |

Qn+1 |

|

|

|

N.V. |

|

|

|

|

|

|

|

|

|

|

|

Qn |

La combinazione S negato e R negato =1 non modifica le uscite, che vengono memorizzate al precedente valore.

Gli ingressi S negato e R negato sono ingressi attivi bassi (che si differenziano da quelli alti per la barra sopra di essi), per ottenere degli attivi alti basta negare S e R negato.

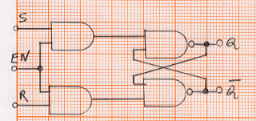

LATCH SR CON ENABLE

L'enable viene indicato o con la sigla E o con la sigla G.

Qui sotto è riportato lo schema elettrico di un Latch SR con enable:

Gli ingressi S e R non sono stati applicati direttamente al Latch SR ma attraverso due porte NAND che hanno lo scopo di abilitare rispettivamente l'ingresso SET e l'ingresso RESET, questa è la tabella di verità di questo particolare Latch SR:

|

E |

S |

R |

Qn+1 |

|

|

X |

X |

Qn |

|

|

|

|

N.V. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Qn |

Qui notiamo che incontriamo delle X nell'ingressi S ed R e si spiega che qualunque sia la combinazione di S ed R, quando E=0 l'uscita rimane invariata.

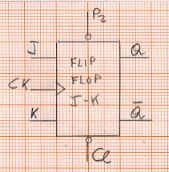

FLIP - FLOP JK

Si definisce flip - flop un elemento di memoria, formato da uno o più latch, il cui funzionamento è sincronizzato da un segnale di clock.

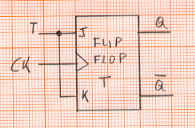

Nel flip - flop nell'istante in cui avviene la commutazione delle uscite è stabilito con certezza, e si evita il difetto di trasparenza, dove trasparenza vuol dire che l'uscita si adegua immediatamente allo stato degli ingressi, ciò è un difetto quando si vogliono circuiti perfettamente sincronizzati, nei quali istanti di commutazione devono essere decisi con precisione. Ecco lo schema del flip - flop JK:

In questo particolare circuito notiamo che l'ingresso J corrisponde al SET del latch SR, mentre l'ingresso K corrisponde al RESET del latch SR.

L'ingresso di clock CK è ciò che fa commutare il circuito durante il fronte di salita dell'impulso di clock.

Quell'ingresso denominato PR è il PRESET che pone l'uscita Q=1 indipendentemente dagli ingressi e dal clock.

Invece l'ingresso opposto al PRESET, denominato CL è il CLEAR che pone l'uscita Q=0 indipendentemente dagli ingressi e dal clock.

La presenza del clock rende il circuito di tipo sincrono: un circuito si dice sincrono quando l'uscita si adegua allo stato degli ingressi solo all'arrivo di un impulso di sincronismo, mentre i circuiti asincroni sono quei circuiti che si adeguano allo stato degli ingressi senza attendere il consenso di un segnale di sincronismo.

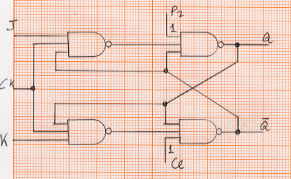

Ecco lo schema elettrico del flip - flop JK:

Ecco la tabella di verità:

|

CK |

J |

K |

Qn+1 |

|

|

X |

X |

Qn |

|

|

|

|

Qn |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Qn |

Il simbolo indica il fronte di salita dell'impulso di clock. In assenza di clock l'uscita resta invariata.

Si può notare, come ho già detto, che il flip - flop JK (a parte per il clock) ricorda molto da vicino la tabella di verità del Latch SR.

FLIP FLOP D

Il flip flop D ha lo scopo di trasferire all'uscita Q il dato presente in ingresso quando arriva l'impulso di clock.

Ecco lo schema:

Notiamo la presenza di un NOT e fa in modo che l'ingresso K sia sempre l'opposto dell'ingresso J. Ecco la tabella di verità:

|

CK |

D |

Qn+1 |

|

|

X |

Qn |

|

|

|

|

|

|

|

|

La lettera D sta per dato.

Un flip - flop di tipo D è un elemento di memoria, il dato in ingresso su D lo trasferisce uguale all'uscita Q, quando arriva il segnale di clock (in questo caso sul fronte di salita).

FLIP FLOP T

Ecco lo schema del flip - flop T:

Come possiamo notare gli ingressi J e K sono collegati tra di loro, mantenendo a livello alto l'ingresso T, ad ogni impulso di clock l'uscita commuta.

Ecco la tabella di verità:

|

CK |

T |

Qn+1 |

|

|

X |

Qn |

|

|

|

Qn |

|

|

|

Qn |

|

Privacy |

Articolo informazione

Commentare questo articolo:Non sei registratoDevi essere registrato per commentare ISCRIVITI |

Copiare il codice nella pagina web del tuo sito. |

Copyright InfTub.com 2024